[Akira Fukuda's Semi -Conchange Industry's Best Line] 3D NAND flash technology with 10Gbit in 1mm square -PC Watch

3D NAND flash memory turned into a skyscraper

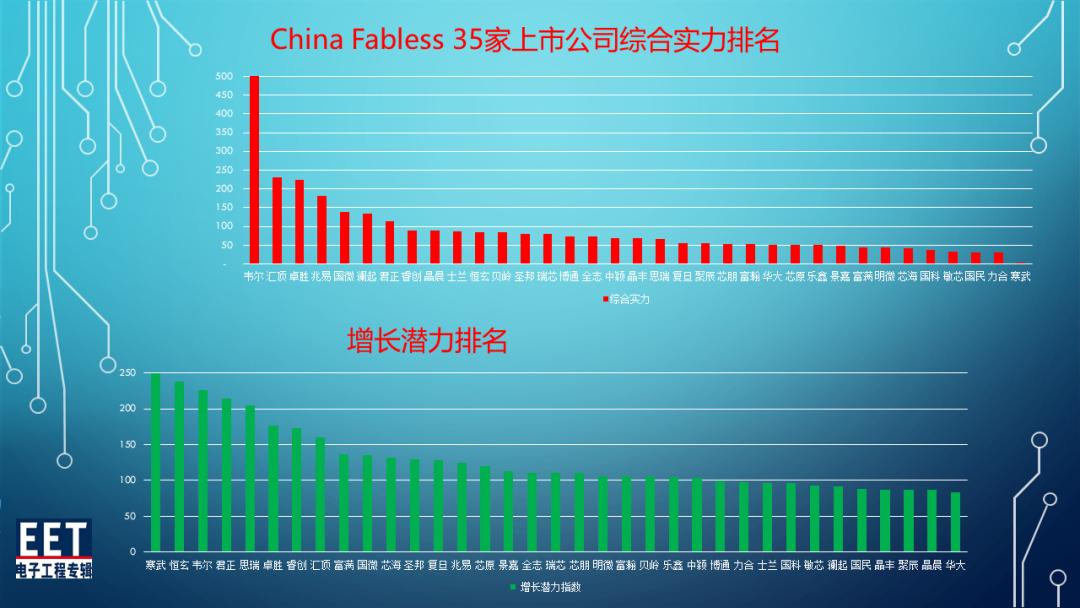

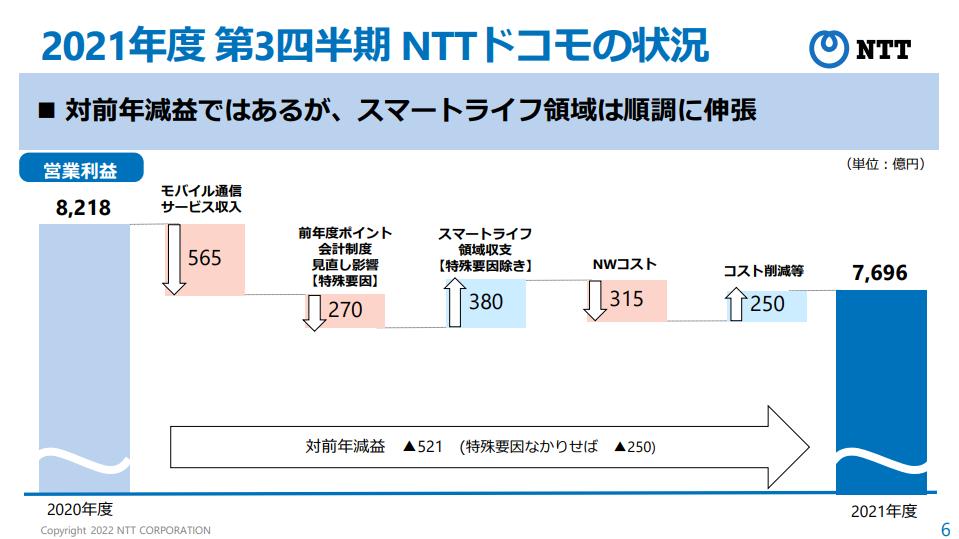

ワード線の積層数が100層を超える超高層3D NANDフラッシュメモリの開発(試作)例。半導体回路技術の国際学会「ISSCC」の発表論文から筆者がまとめた3D NAND flash memory is not stopped.The vertical Celtransistor's number of stacks and the number of diles of the word line reached the maximum, reaching 176 layers.In the spring of last year (2019), it was up to 128 layers, so the number of laminated layers in two years is 1..It increased 375 times.

High -rise flash memory is often compared to high -rise building.It was in 2019 that it exceeded 100 stories.And this year (2021), it became 176 floors.It is certain that next year (2022) or again (2023) will be over -the -rise buildings over the 200th floor.

The more terrific pace of memory density (memory capacity/silicon die area) is more terrific than high -rise.In the spring of 2021, the memory density is 4bit/cell (QLC) method 13.8Gbit/square mm, 3bit/cell (TLC) method 10.8Gbit/square mm reached.

The highest record in the past is the QLC method 8.9Gbit/square mm (spring 2020), TLC method 7.8Gbit/square mm (spring 2019).1 each.55 times, 1.Improved 38 times.You can remember more than 10Gbit data in silicon with only 1 mm square.

The memory density of the NAND flash memory announced at the International Society of Semiconductor Circuit Technology ISSCC is 31 in 10 years from 2011 to 2021..Improved 4 times.In the annual rate conversion, 1.This means that it has increased in 41 times/year.It has continued its high growth of "about 2 times in two years" and "about four times in four years".

NANDフラッシュメモリの記憶密度推移(2011年~2021年、線形目盛り)。半導体回路技術の国際学会「ISSCC」の発表論文から筆者がまとめたNANDフラッシュメモリの記憶密度推移(2011年~2021年、対数目盛り)。半導体回路技術の国際学会「ISSCC」の発表論文から筆者がまとめた